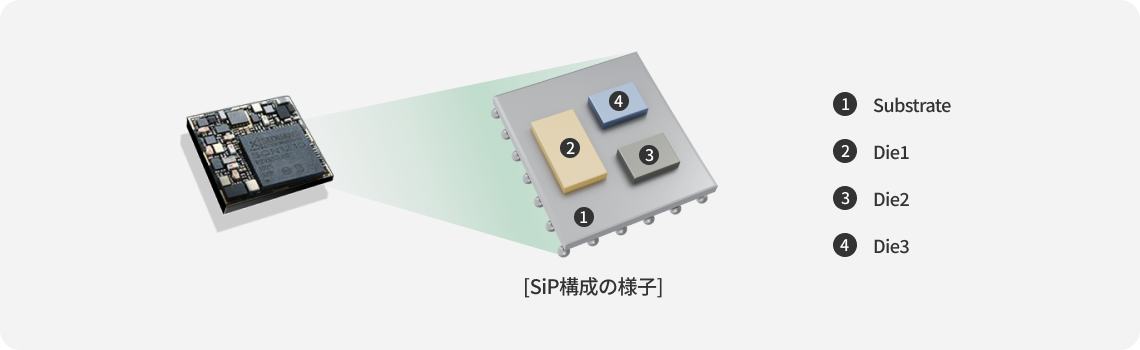

システムを実現できるパッケージ基板

パッケージの中に複数のICやPassive Componentが実装されており、複合的な機能を一つのシステムで実現する製品です。また、

PA(Power Amplifier)のような製品に使われ、放熱の特性があります。製品シリーズには、Flip-Chip SiPとCorelessがあります。

小型化

複数のICと受動素子が一つのモジュールに統合され、パッケージを小型化できます。

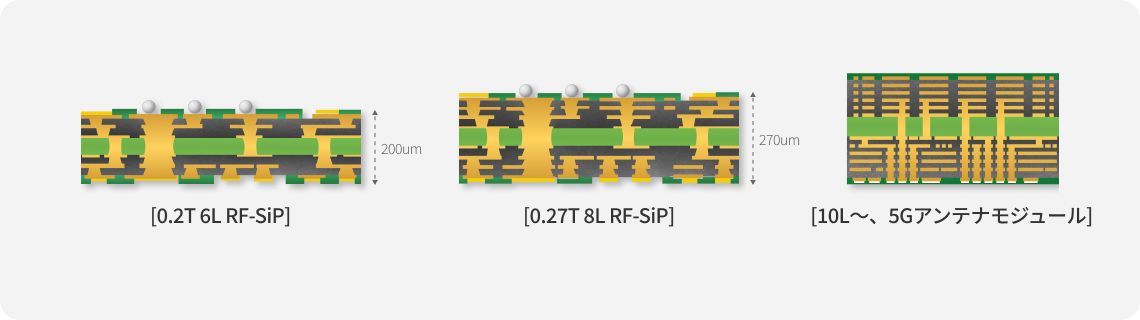

薄板の具現

超薄板の駆動性を確保することで0.2mmの厚さの基板(6層基準)を具現できます。

主なコア技術

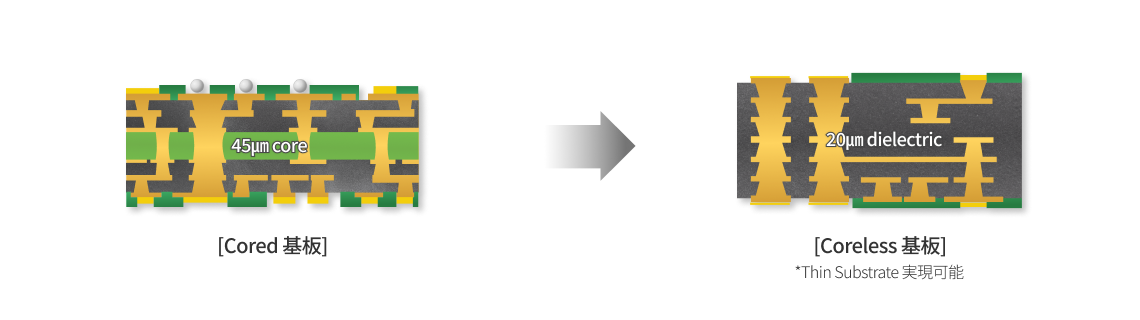

Coreless RF-SiP

Coreless工法により絶縁の厚みを削減し、EMI(Electro Magnetic Interference)及びParasitic Inductanceを制御して信号の特性を向上で

きることから、Thin Substrateを実現可能です。

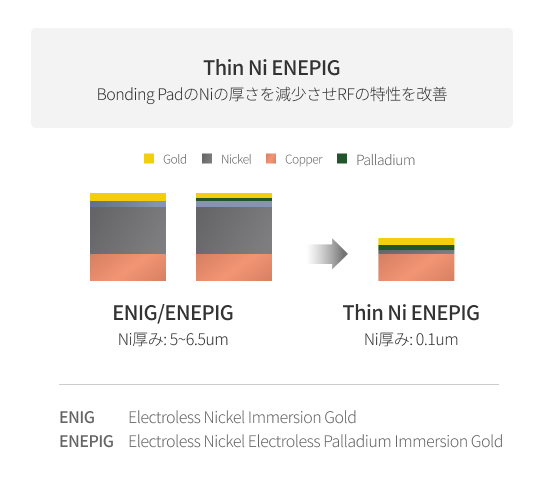

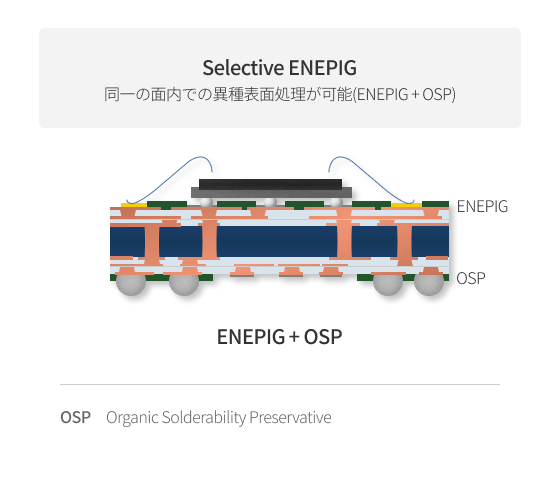

ENEPIGの表面処理

ENEPIGの表面処理技術は下記のような特性があります。

SiP Lineup

Lineup by Specification

| Layer Structure | Cored | 2L / 4L / 6L / 8L / 10L (Mass Production) | + 12L / 14L (Sample Available) |

|---|---|---|---|

| Coreless | 5L / 6L / 7L / 8L (Mass Production) | + 4L / 9L / 10L (Sample Available) | |

| Line Width / Space | 12 / 16um (Mass Production) | 10 / 15um (Sample Available) | |

| Bump Pitch | 130um (Mass Production) | 105um (Sample Available) | |

| Surface Finish | Direct Au, Thin ENEPIG, Selective ENEPIG (Mass Production) | Direct Au, Thin ENEPIG, Selective ENEPIG (Sample Available) | |

* umは、㎛を意味します。